一、CPU发展历史

中央处理器(CPU),这颗被誉为计算机“大脑”的微小芯片,其发展历程波澜壮阔,是一部浓缩了人类智慧、科技突破与商业博弈的壮丽史诗。从远古的计算器具到如今驱动万物互联的智能核心,CPU的每一次革新都深刻地改变着世界。回顾这段历史,不仅能让我们理解CPU技术的来龙去脉,更能从中汲取宝贵的经验与启示,洞察其未来的发展脉络。

1.1 启蒙时代:从算盘到继电器

在CPU真正诞生之前,人类对于计算的追求早已绵延数千年。这段漫长的启蒙时代,是CPU思想的萌芽与早期计算技术的积累阶段,为后续的飞跃奠定了坚实的基础。

古代计算工具的智慧结晶: 追溯计算工具的源头,中国的算盘以其珠算体系体现了数值表示与运算的基本逻辑。西方的安提基特拉机械则被视为最早的模拟计算机,其复杂的齿轮结构展现了早期机械自动化计算的尝试。这些古老的工具,是人类利用物理装置辅助思考、解决复杂计算问题的最初探索。

图 1 两千年前古希腊的安提基特拉机械计算机

机械计算机的先驱探索: 随着科学技术的进步,17世纪法国科学家布莱斯·帕斯卡发明了机械加法器,德国数学家戈特弗里德·威廉·莱布尼茨则制造出能进行乘除运算的“步进计算器”。19世纪英国数学家查尔斯·巴贝奇提出的差分机和分析机构想,在理念上已接近现代通用计算机,分析机设想了输入、存储、处理、控制和输出五部分,并引入了程序控制概念。尽管巴贝奇未能完全实现,但其思想超越了时代。阿达·洛芙莱斯为分析机编写算法,被誉为首位程序员,预见到计算机的多功能性。

电子管与晶体管的革命性突破: 机械计算机的局限催生了电子学的应用。电子管的出现使电流通断表示二进制成为可能,运算速度大幅提升。ENIAC作为第一台电子数字计算机,使用了大量电子管,体积庞大,功耗高且可靠性不佳。

图 2 ENIAC庞大机房

1947年贝尔实验室发明的晶体管,凭借体积小、功耗低、寿命长等优点,迅速取代电子管,引领计算机进入小型化、高速化和高可靠性的新时代,为集成电路和微处理器的诞生铺平了道路。

1.2 微处理器的诞生与仙童的“八叛逆”

晶体管虽是飞跃,但分立元件构建复杂系统效率低、可靠性差。集成化需求催生了集成电路(IC),并最终孕育出微处理器。仙童半导体及其“八叛逆”在此过程中扮演了关键角色。

集成电路的曙光: 1958年,德州仪器的杰克·基尔比和仙童半导体的罗伯特·诺伊斯几乎同时独立发明了集成电路。诺伊斯基于硅的平面工艺方案更易批量生产,奠定了现代IC制造基础。两人的发明开启了微电子技术新纪元。

仙童“八叛逆”与硅谷传奇: 威廉·肖克利创办的肖克利半导体实验室吸引了众多天才,但因管理问题,八位核心成员(包括戈登·摩尔、罗伯特·诺伊斯)于1957年出走,创办仙童半导体,被称为“八叛逆”。仙童率先采用平面工艺,培养了大量人才,成为“硅谷黄埔军校”,催生了英特尔、AMD等众多公司,深刻影响半导体产业。

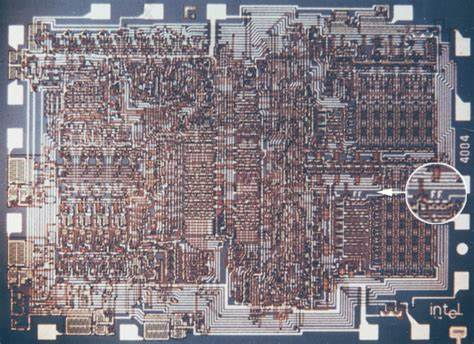

英特尔与4004的问世: 1968年,戈登·摩尔和罗伯特·诺伊斯创办英特尔。1969年,日本计算器公司委托英特尔设计芯片。工程师特德·霍夫提出通用可编程逻辑芯片方案,斯坦利·马泽尔完善,费德里코·费金凭借硅栅技术成功将其集成。1971年11月15日,英特尔4004发布,这是世界首款商用微处理器,将CPU功能集成到单芯片上,标志着计算机核心部件的重大变革,为计算机小型化、廉价化和普及化打开了大门。

图 3 Intel 4004芯片

早期微处理器的群雄逐鹿: 4004之后,英特尔迅速推出8位处理器8008(1972年)和更强大的8080(1974年),后者被认为是首款可用于通用计算的微处理器。摩托罗拉于1974年推出MC6800,成为8080的有力竞争者。前英特尔工程师费金创立的齐洛格公司于1976年推出Z80,兼容8080并有所增强,取得了巨大商业成功。MOS Technology的6502处理器(1975年)因其简洁高效且价格低廉,成为Apple I/II、Commodore PET等早期畅销PC和游戏机的核心,推动了个人电脑革命。70年代,德州仪器(TMS9900,首款16位微处理器)、国家半导体等也参与竞争,市场百花齐放,为个人计算机时代奠定了技术基础。

1.3 x86王朝的奠基与巩固

80年代见证了英特尔x86架构在个人计算机领域的崛起和统治。这一王朝始于一次关键的商业合作,并通过持续演进和市场策略得以巩固。

8086/8088与IBM PC的联姻: 1978年,英特尔发布16位处理器8086,随后推出外部8位数据总线的8088,以降低系统成本。IBM为快速进入个人计算机市场,打破传统,采取开放架构和外部采购策略。因供货、价格及8088的成本优势,IBM选择了8088作为其首代个人计算机IBM PC 5150的核心。1981年IBM PC的发布成为分水岭,其巨大成功及后续兼容机的出现,使x86架构成为PC领域主流,奠定了英特尔的领导地位。

x86架构的持续进化: 个人计算机市场发展推动CPU性能需求。1982年,英特尔推出80286,引入保护模式和MMU,支持更大内存和多任务操作系统,用于IBM PC/AT。1985年,发布32位处理器80386DX,可寻址4GB物理内存,引入虚拟8086模式,标志着x86进入32位时代,为Windows等图形操作系统普及奠定基础。80386SX作为低成本版本加速了市场过渡。

奔腾时代与多媒体扩展: 1989年发布的80486集成了FPU和一级缓存。1993年,英特尔推出全新品牌Pentium(奔腾),采用超标量架构,性能大幅提升。此后Pentium Pro、Pentium II/III/4等产品接踵而至,不断提升主频、缓存,并引入MMX、SSE等多媒体指令集。

竞争者的挑战:AMD的崛起: 英特尔在巩固x86王朝时面临AMD等公司的挑战。AMD从第二供应商转向自主研发,凭借Am386、K5、K6等产品站稳脚跟。1999年,AMD推出Athlon(速龙),性能一度超越同期奔腾III,打破英特尔高端垄断。后续的Athlon XP、Athlon 64(率先引入64位桌面扩展)持续施压。AMD的竞争迫使英特尔加快创新,也使消费者受益。Cyrix、VIA等公司也曾参与市场竞争。尽管面临挑战,凭借先发优势、技术创新、制造能力、Wintel联盟及市场策略,英特尔x86架构始终主导PC领域。

1.4 指令集之争:CISC与RISC的较量

CPU发展中,关于设计哲学的探讨从未停止,CISC与RISC之争影响深远。

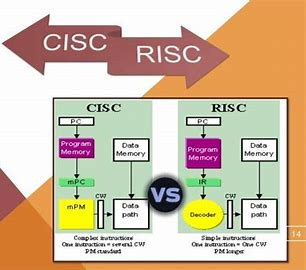

CISC的复杂性与RISC的简洁高效: CISC(复杂指令集计算机)设计思想源于早期内存昂贵、编译器不成熟的背景,倾向于将复杂功能集成到硬件指令,一条指令可完成多操作。x86是典型代表,指令集庞杂但向后兼容。其优点是特定任务效率高,缺点是指令变长解码复杂、执行周期不一、芯片设计难、常用指令占比不高。

RISC(精简指令集计算机)基于“80/20”原则(80%任务由20%简单指令完成)提出。核心思想包括:精简指令集、固定指令长度、单周期执行、Load/Store架构、大量通用寄存器、强调编译器优化。RISC优势在于简洁高效,易于实现高主频和深流水线,提升IPC。

图 4 CISC对比RISC

ARM架构的崛起与移动时代的来临: RISC理念催生了MIPS、SPARC等,但ARM架构真正将其发扬光大。ARM(Advanced RISC Machines)源于英国Acorn公司,1985年诞生ARM1。ARM从始至终以低功耗、小尺寸、高性能为目标,其IP授权商业模式促进了生态繁荣。移动互联网时代,ARM凭借低功耗优势及不断演进的性能,完美契合移动设备需求,几乎垄断移动芯片市场(苹果A系列、高通骁龙、三星Exynos、华为麒麟、联发科天玑等)。

x86架构的RISC化内核探索: 面对RISC挑战,x86厂商如英特尔从Pentium Pro开始,在处理器内部引入类似RISC的微操作(μops)内核。外部CISC指令解码为内部RISC风格微操作,在后端以RISC方式优化执行。这种“CISC外壳,RISC内核”设计使x86在保持兼容性的同时借鉴RISC效率。现代高性能x86处理器已是CISC与RISC技术融合的产物。CISC与RISC之争是不同场景下的权衡,CISC在PC/服务器领域主导,RISC(ARM)在移动/嵌入式领域领先。RISC-V等开源指令集的兴起使这场争论以新形式继续。

1.5 多核并行与异构计算的浪潮

21世纪,CPU发展遇主频提升瓶颈(功耗墙、散热墙),单核性能提升放缓。多核CPU和异构计算成为主流。

单核性能瓶颈与摩尔定律的延伸: CPU性能曾依赖主频增长,但功耗和散热限制了单纯提高主频的道路(频率墙)。晶体管数量虽按摩尔定律增加,但用于传统单核性能提升的方法边际效应递减。如何有效利用新增晶体管成为核心问题。

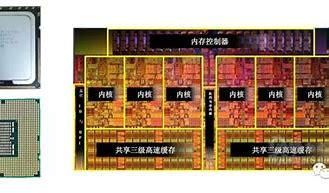

多核心CPU的普及与挑战: 多核CPU通过并行处理提升系统吞吐率和响应速度。2005年前后,英特尔(Pentium D, Core Duo)和AMD(Athlon 64 X2)推出首批商用双核桌面CPU,PC进入多核时代。随后四核、八核乃至更多核心普及。服务器领域多核/众核成为标配。 多核优势: 提升并行处理能力、改善多任务体验、特定应用性能飞跃。 多核挑战: 软件并行化难度(阿姆达尔定律限制)、核间通信与数据一致性(MESI协议)、功耗与散热管理。

图 5 多核心CPU的裸晶照片

GPU、NPU等异构单元的融合趋势: 异构计算(Heterogeneous Computing)指系统中使用不同类型计算单元(CPU, GPU, DSP, FPGA, ASIC等)协同工作。GPU凭借大规模并行处理单元,在GPGPU技术(CUDA, OpenCL)推动下,广泛用于科学计算、AI(深度学习训练与推理)。NPU(神经处理单元)或AI加速器针对神经网络运算深度优化,低功耗提供强大AI算力。现代高端CPU(尤其SoC)已是集成CPU核、GPU核、NPU核、ISP、DSP等的复杂异构系统。 异构融合优势: 能效最大化、性能提升、系统集成度提高。 异构计算挑战: 编程模型复杂、任务调度、单元间数据共享与通信效率。CPU发展从单核主频、多核并行到异构融合,始终围绕提供更强、更高效、更智能的计算能力演进。

1.6 思考与展望:CPU历史给我们的启示

回顾CPU发展史,不仅是技术梳理,更是启迪之旅,蕴含技术演进规律、市场选择机制和创新力量,为理解当前和展望未来提供视角。

技术迭代与市场选择的规律: CPU发展展现技术迭代加速趋势,从元件革命到微处理器内部架构演进。市场选择扮演关键角色,IBM PC选择8088奠定x86地位,移动时代低功耗需求推高ARM。单纯技术先进非唯一标准,成本、功耗、生态、商业联盟、时机等均是关键因素。技术需适应市场和趋势,否则可能被边缘化。

开放与封闭生态的博弈: IBM PC开放架构催生庞大兼容市场和Wintel联盟,加速PC普及但也使IBM失主导权。苹果Mac坚持软硬一体封闭生态,凭体验和利润独树一帜,自研M系列芯片彰显协同优化潜力。ARM的IP授权模式是独特“授权开放”,保证架构统一又鼓励下游创新。开放易扩张但也可能碎片化;封闭易优化但也可能生态建设慢。未来可能开放与封闭并存融合,如RISC-V的完全开放带来新变量。

对未来CPU发展方向的初步思考: 能效比持续提升: 移动计算、物联网、边缘计算及数据中心节能需求,使性能功耗比(Performance per Watt)成核心目标。需制程、架构、电源管理、异构集成创新。 异构集成与专用化成主流: 通用CPU仍重要,但面对AI、大数据等特定需求,集成DSA的异构SoC更具优势。CPU更多扮演“指挥官”。Chiplet技术为异构集成提供更灵活经济方案。 软件定义和硬件可重构性或带来突破: 软件定义硬件或FPGA等可重构技术,使硬件按需动态调整,提升灵活性。 超越冯·诺依曼架构的探索值得关注: “存储墙”瓶颈凸显。存内计算(PIM)、神经形态计算、量子计算等为突破极限提供路径。 安全性与可信计算上升到前所未有高度: 万物互联时代,CPU安全直接关系数字社会安全。硬件级可信根、防御侧信道攻击、数据隐私等成关键考量。 CPU发展史是不断挑战极限、追求创新的历史。展望未来,虽面临挑战,但对更强计算能力的渴望永无止境。借鉴历史,拥抱新技术,CPU传奇将继续,为社会数字化转型提供动力。

二、CPU原理介绍

本章将深入CPU内部,揭示其基本组成、指令执行奥秘,介绍流水线、缓存等关键技术,以及分支预测、超标量、乱序执行等提升性能的先进理念,帮助读者构建对CPU工作原理的系统认知。

2.1 CPU的基本组成:运算器、控制器与存储器

CPU主要集成了冯·诺依曼结构中的运算器、控制器以及一部分高速缓存。

冯·诺依曼体系结构回顾: 该结构核心思想是“存储程序控制”,计算机由运算器、控制器、存储器、输入和输出设备组成,指令和数据以二进制形式同等存于存储器中,按地址寻访。CPU是执行指令、处理数据的核心。

运算器(ALU)的功能与逻辑门: 运算器(ALU)执行算术运算(加减乘除、浮点)和逻辑运算(与或非、移位、比较)。ALU由大量逻辑门(与门、或门等)组成,内部含累加器、通用寄存器、状态寄存器等,暂存操作数、结果及状态。控制器将数据送入ALU,指定运算,结果送回寄存器或内存。ALU是CPU的“计算核心”。

控制器(CU)的指令解码与时序控制: 控制器(CU)是CPU的“大脑”,根据指令生成控制信号,指挥各部件协同工作。核心职责包括:取指令(Fetch)、指令译码(Decode)、发出控制信号(Issue Control Signals)、控制程序流程(处理分支、循环、中断)。内部含指令寄存器(IR)、程序计数器(PC)、时序控制逻辑和指令译码器。现代CPU控制器设计复杂,采用微程序或硬布线逻辑,结合流水线、分支预测等技术。

寄存器组(Registers)的作用与分类: 寄存器是CPU内部高速存储单元,访问速度远快于内存和缓存,用于临时存放指令、数据、地址和状态信息,减少访存,提高速度。 分类: 通用寄存器(GPRs,如EAX, R0)、程序计数器(PC/IP,存下条指令地址)、指令寄存器(IR,存当前指令)、状态/标志寄存器(Flags,记录运算结果特征和CPU状态)、地址寄存器(段寄存器、栈指针SP、基址指针BP)、控制寄存器(控制CPU工作模式)。寄存器数量和类型是衡量CPU架构的重要指标。

2.2 指令周期:CPU如何执行一条指令

CPU执行程序是不断取指、分析、执行指令的循环。每条指令执行时间为一个指令周期,典型分解为取指、译码、执行、访存(可选)、写回。

取指(Fetch)阶段: 控制器根据PC中地址,从内存或缓存读取指令到IR。PC更新指向下条指令。 译码(Decode)阶段: 指令译码器分析IR中指令,确定操作(Opcode)和操作数位置,生成控制信号。 执行(Execute)阶段: ALU根据控制信号对操作数执行指定操作。算术/逻辑运算结果存回寄存器或临时寄存器。控制转移指令修改PC。 访存(Memory Access)阶段: 仅需读写内存的指令(LOAD/STORE)进入此阶段。CPU与内存/缓存交互数据。 写回(Write Back)阶段: 运算结果或从内存加载的数据写回目标寄存器。完成后,开始下个指令周期。

早期CPU串行执行各阶段,现代CPU采用流水线技术重叠执行。

2.3 流水线技术:提升CPU执行效率的关键

为提高CPU吞吐率,流水线技术(Pipelining)应运而生,借鉴工业装配线思想,将指令执行划分为若干独立子过程(流水线级,如IF, ID, EX, MEM, WB)。

流水线的概念与优势: 每个流水线级由专门硬件负责。多条指令可同时处于不同处理阶段。理想情况下,k级流水线稳定运行时,每时钟周期可完成一条指令的某阶段并输出一条完成指令,吞吐率可达单周期CPU的k倍。 主要优势: 提高指令吞吐率、提高CPU部件利用率、允许更高时钟频率。

流水线冒险(Hazard)及其解决方案: 流水线可能遇冒险(Hazard)或冲突(Conflict),阻碍正常流动。 结构冒险: 多指令同周期需同一硬件资源。解决方案:增硬件资源(如分离I/D Cache)或优化设计。 数据冒险: 后续指令需前面未完成指令的结果(数据依赖)。写后读(RAW): 最常见。解决方案:流水线暂停/插入气泡(Stall/Bubble)、数据前推/旁路(Forwarding/Bypassing,将计算结果直接传给后续指令)、编译器调度(指令重排)。读后写(WAR)、写后写(WAW): 乱序执行中需关注。 控制冒险/分支冒险: 遇分支/跳转指令,CPU难立即确定下条指令地址,致流水线暂停或作废已取指令。解决方案: 流水线暂停、分支预测(Branch Prediction,预测分支结果,错误则Flush流水线并付出Penalty)、延迟分支(Delayed Branch,编译器在分支后插入无论如何都执行的指令填充流水线)。

通过精心设计和有效处理冒险,现代CPU能显著提升指令级并行(ILP)。

2.4 缓存(Cache)系统:弥补内存速度鸿沟

CPU运算速度远超主内存(DRAM)访问速度,形成“内存墙”。为弥补此差距,CPU集成多级高速缓存(Cache)。

缓存的工作原理与局部性原理: 缓存是小容量、高速度存储器,存主内存部分数据副本。CPU访存先查缓存,命中(Hit)则直接快速读取;未命中(Miss)则访主内存,加载数据块到缓存备用。 有效性依赖局部性原理:时间局部性: 被访问数据项不久可能再被访问(如循环变量)。空间局部性: 被访问数据项的相邻数据项不久可能被访问(如数组顺序访问)。未命中时调入整个数据块(Cache Line)利用此特性。

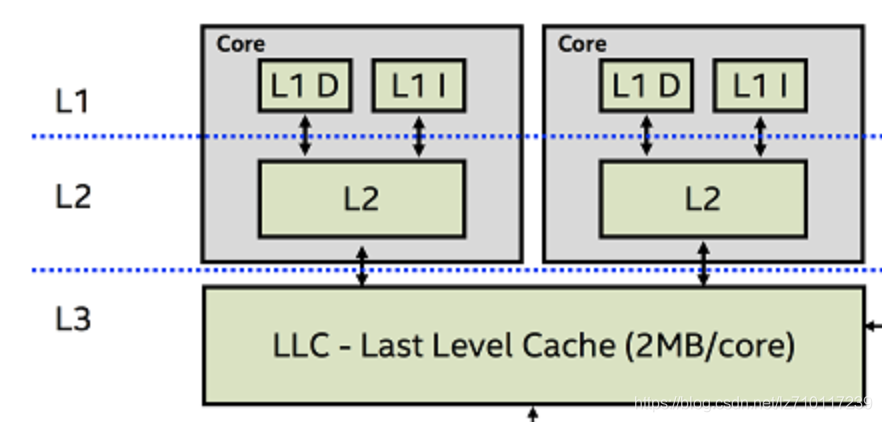

L1, L2, L3多级缓存的结构与作用: 现代CPU常采用三级缓存:L1 Cache: 最靠近核心,容量最小(几十至几百KB),速度最快(几周期延迟)。常分指令缓存(L1 I-Cache)和数据缓存(L1 D-Cache),核心独享。L2 Cache: 容量比L1大(几百KB至几MB),速度比L1慢但远快于主内存。可核心独享或部分核心共享。L3 Cache: 容量最大(几MB至几十MB),速度相对L1/L2慢但仍远快于主内存。通常CPU所有核心共享,利于核间数据共享和通信。 CPU依次查找L1、L2、L3,未命中才访主内存。数据从主内存加载时通常填充各级缓存。

缓存一致性协议(MESI等)简介: 多核CPU中,各核私有缓存和共享缓存/主内存间需保持数据一致性。缓存一致性协议解决此问题。MESI协议(Modified, Exclusive, Shared, Invalid)是常用写失效协议,为每缓存行维护一状态位。核心读写缓存行时,据当前状态和操作类型,遵循协议转换状态,并通过总线与其他核心通信,确保数据一致。

图 6 CPU多级缓存示意图

高效缓存系统显著减少CPU平均内存访问时间,充分发挥运算潜力。

2.5 先进技术简介:分支预测、超标量与乱序执行

为进一步挖掘ILP,突破流水线瓶颈,现代CPU采用分支预测、超标量和乱序执行等先进技术。

分支预测(Branch Prediction)的重要性: 控制冒险(尤其条件分支)影响流水线效率。分支预测器在分支指令实际执行前预测其结果,让CPU投机性(Speculatively)执行预测路径指令。类型: 静态预测(规则简单)、动态预测(基于分支历史表BHT)。高级动态预测器结合全局或模式历史。分支目标缓冲器(BTB)存储跳转目标地址。结果: 预测正确则流水线顺畅;错误则需撤销(Flush)错误路径指令,重新取指,产生分支预测惩罚(Misprediction Penalty)。高准确率(常>90%)对性能至关重要。

超标量(Superscalar)架构: 允许CPU一周期内同时发射和执行多条指令。通过在核心内设多个并行执行单元(整数ALU, FPU, Load/Store单元等)实现。前端(取指/译码)也需增强以支持多指令处理。指令调度器分派无依赖且资源可用的指令并行执行。4发射超标量处理器理想IPC可达4。实际IPC受程序并行性、依赖、预测准确率等影响。

乱序执行(Out-of-Order Execution, OoOE)的智慧: 即使超标量,顺序执行也可能因指令阻塞而限制并行性。OoOE允许CPU打破原始顺序,在不违背数据依赖前提下,动态重排指令执行顺序,让已就绪指令优先执行。核心思想: 顺序取指/译码,乱序执行,顺序提交(In-order commit/retire)。指令译码后入指令缓冲池(保留站/指令窗口)。调度器监控指令,操作数就绪且执行单元可用即可发射。结果暂存重排序缓冲器(ROB)。最后结果按原始顺序从ROB提交到架构寄存器/内存,确保行为一致并精确处理异常。 OoOE通过越过阻塞指令执行后续独立指令,极大提高执行单元利用率和ILP,是现代高性能CPU标配。需复杂硬件(寄存器重命名、ROB等)管理。

这些先进技术结合,使现代CPU每周期执行多条指令,持续提升实际应用性能。

2.6 思考与展望:CPU原理的演进与未来

CPU设计是在性能、功耗、成本、复杂度间不断权衡的艺术。经典原理奠定基础,但也面临新挑战,催生对未来计算范式的探索。

现有原理的局限性探讨:冯·诺依曼瓶颈(存储墙): CPU与内存速度差距仍是瓶颈。数据搬运耗时耗能。功耗墙与散热墙: 功耗密度和总功耗仍是巨大挑战。指令级并行的极限: 程序固有依赖限制ILP,阿姆达尔定律揭示串行部分制约。暗硅(Dark Silicon)问题: 功耗限制使部分晶体管无法同时全性能运行,造成资源浪费。编程复杂性: 发挥多核、异构硬件性能,并行编程难度增加。

新型计算范式对CPU原理的潜在影响:存内计算(PIM)/近存计算(NMC): 计算逻辑集成到存储芯片内或近处,减少数据搬运,突破存储墙。神经形态计算: 借鉴生物大脑,设计类脑芯片,擅长认知任务,可能作协处理器。量子计算: 利用量子特性,在特定问题上提供超强算力。成熟后将对计算领域产生革命性影响。光计算/光互连: 光子代替电子传输/计算,具高带宽、低延迟、低功耗潜力,望解决通信瓶颈。可重构计算: 基于FPGA等,硬件功能运行时按需动态配置,提供灵活性与效率。 新兴范式多为CPU补充或加速器,形成多样化异构生态。CPU未来更强调作控制核心、任务调度及与专用单元高效协同。CPU原理演进将从追求通用性能转向关注能效、智能及与新兴技术融合。

理解CPU工作原理是对现有技术的掌握,更是洞察未来趋势的起点。CPU内涵和外延将持续演变,驱动计算世界向更高效、智能、普惠发展。

三、CPU性能参数

理解CPU各项性能参数及其相互关系,有助于科学评估CPU性能,并在选购时做出明智决策。

3.1 主频(Clock Speed):速度的象征与误区

主频,也称时钟频率,以吉赫兹(GHz)为单位,代表CPU内部主时钟信号频率。

主频的定义与单位(GHz): CPU主时钟如节拍器,控制同步工作节奏。每周期晶体管开关一次。主频越高,单位时间周期数越多,理论上执行指令越快。

主频与实际性能的关系:IPC的重要性: 主频仅代表“心跳速度”,非完全决定“工作效率”。实际性能是主频与IPC(每周期执行指令数)的乘积。IPC取决于微架构设计(流水线、超标量、乱序、分支预测、缓存等)。同主频不同架构CPU,IPC可能差异巨大,致性能迥异。比较不同架构或代际CPU时,单纯比较主频无意义。

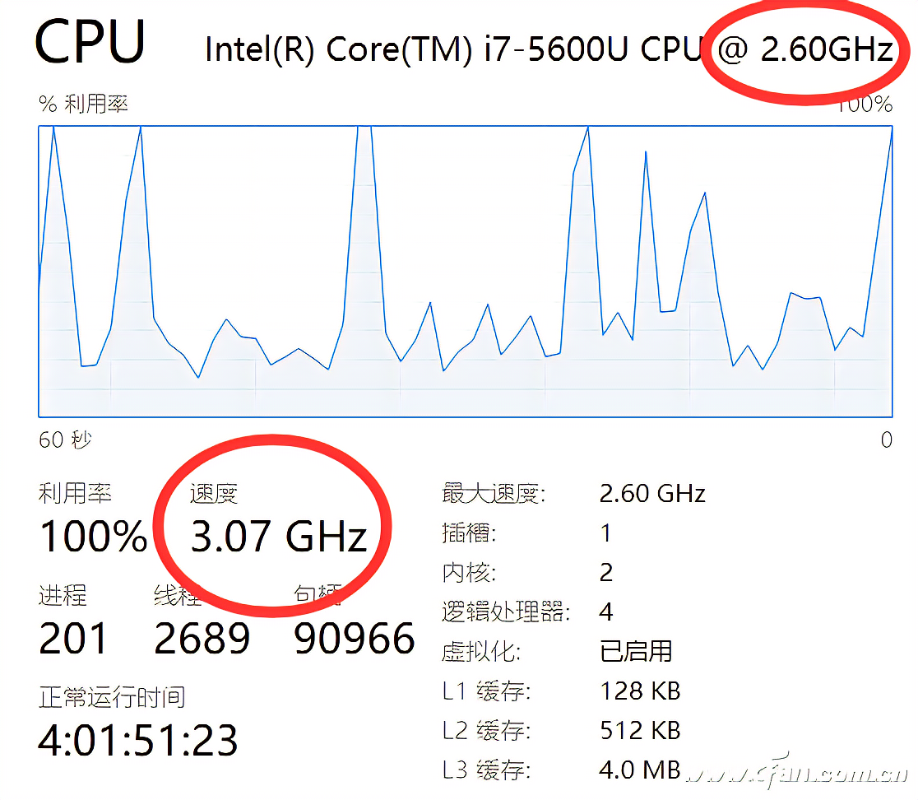

动态频率调整技术(Turbo Boost/Precision Boost): 现代CPU普遍采用此技术平衡性能与功耗。允许CPU在散热和功耗允许范围内,据负载自动提升一或多核频率,提供更高瞬时性能。负载降低或温度过高则频率回落。使主频变为动态范围(基准频率与最大睿频)。

图 7 CPU在“睿频”模式下主频动态变化的曲线图

主频是重要参考,但需结合IPC及其他参数综合评估。

3.2 核心数(Cores)与线程数(Threads):并行处理能力

多核CPU已成主流,核心数和线程数是衡量并行处理能力的关键。

物理核心与逻辑核心(超线程技术):物理核心: CPU芯片上真实存在的、能独立执行指令的处理单元。各有完整执行资源。逻辑核心/线程数: 通常与同步多线程(SMT)技术相关(如英特尔超线程HT)。SMT允许一物理核心模拟出多个逻辑核心,利用物理核心执行单元在处理单线程时可能存在的空闲周期,插入另一线程指令,提高资源利用率。4核8线程CPU即4物理核,每核可处理2线程。 逻辑核心性能不如独立物理核心,因共享资源。但在某些多线程优化场景下,超线程能带来一定性能提升(约10%-30%)。

多核心对不同应用场景的影响: 多核CPU对能有效利用并行处理的应用(视频编辑、3D渲染、科学计算、虚拟机)及多任务环境,性能提升显著。对主要依赖单线程性能的应用(老旧游戏、特定计算软件),增加核心数收益有限,单核性能(IPC和主频)更重要。

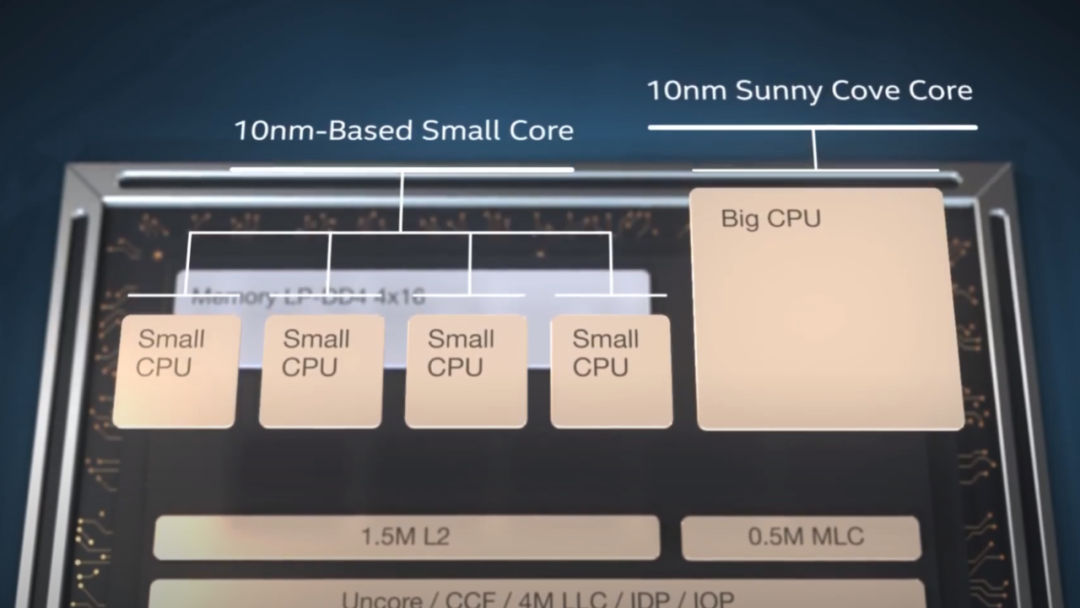

大小核架构(Performance-cores & Efficiency-cores): 为平衡高性能和低功耗,混合架构流行(如英特尔P-cores+E-cores,ARM big.LITTLE)。P核(大核)专注极致性能,E核(小核)低功耗处理后台和轻载任务,优化整体能效。操作系统和硬件调度器需协同智能分配任务。

图 8 大小核示意图

核心数和线程数增加带来更强并行处理能力,但也对软件并行化设计提更高要求。

3.3 每周期指令数(IPC, Instructions Per Clock):架构效率的体现

IPC(每时钟周期平均执行指令数)是衡量CPU微架构效率的核心指标。

IPC的定义及其影响因素: CPU实际性能 ≈ 主频 × IPC。主频相近时,IPC越高,性能通常越强。IPC高低主要取决于微架构设计:流水线效率、超标量与乱序能力、分支预测准确率、缓存系统性能、指令集架构(ISA)、内部总线与互联等。

如何理解IPC在性能评估中的作用: IPC非CPU规格表上固定值,而是通过基准测试计算的平均值。同一CPU运行不同程序IPC可能不同。对同代或相邻代同架构CPU,IPC提升是衡量架构改进的重要标志。厂商宣称的“同频性能提升百分之多少”主要指IPC提升。

理解IPC重要性助摆脱“唯主频论”,认识CPU性能本质在于高效执行指令。

3.4 缓存(Cache):容量、速度与延迟

缓存系统是CPU性能关键组成,直接影响数据获取效率。关注参数:容量、速度、延迟。

L1, L2, L3缓存的典型容量与速度范围:L1 Cache: 容量小(每核D-Cache/I-Cache各32KB-128KB),速度极快(延迟3-5周期)。L2 Cache: 比L1大(每核256KB-2MB,或少数核共享更大L2),速度比L1慢(延迟10-20周期)。L3 Cache/LLC: 容量最大(CPU内所有核心共享,几MB至几十MB,服务器CPU可上百MB),速度相对L1/L2慢(延迟30-60周期),但仍显著快于主内存。 具体CPU型号配置不同。缓存容量越大,命中率通常越高,但芯片面积、功耗和延迟也可能增加。

缓存延迟对性能的实际影响: 缓存延迟指CPU发请求到收数据时间。低延迟对性能至关重要。L1极低延迟保证最常用数据/指令快速访问,L2/L3作后续防线,减少访主内存。

智能缓存技术与共享机制:动态共享缓存: L3通常所有核心共享,允许核心按需动态使用更多空间。预取技术(Prefetching): CPU预测未来可能需数据,提前从主内存加载到缓存。高效替换算法(Replacement Algorithms): 如LRU,决定缓存满时替换哪些旧数据块。非包含式/包含式/排他式缓存: 定义不同级缓存间数据内容关系策略。

更大缓存容量、更低延迟和更智能管理机制,构成高性能CPU缓存系统基础。

3.5 制造工艺(Process Node):纳米竞赛与物理极限

制造工艺是决定CPU晶体管密度、功耗和性能潜力的基础物理参数,通常以“纳米”(nm)衡量。

工艺节点的含义(nm)及其演进: 工艺节点(如14nm, 7nm, 3nm)传统指晶体管最小特征尺寸。数字越小,意味更高晶体管密度或更小芯片面积,通常伴随开关速度提升和功耗降低。是摩尔定律延续关键。随节点缩小,命名方式渐不严格对应实际物理尺寸,更多成技术代号。不同代工厂定义和实际性能可能存差异。

先进工艺对功耗、性能、核心密度的影响:更高晶体管密度: 可集成更多核心、更大缓存或更复杂逻辑。更低功耗: 小晶体管开关能耗少。更高性能: 小晶体管开关快,助提升频率和IPC。 但工艺进入个位数纳米,物理极限挑战大(量子隧穿、漏电、制造难度和成本剧增)。

FinFET、GAA等晶体管结构的革新: 为克服传统平面晶体管挑战,结构不断革新。FinFET(鳍式场效应晶体管): 22/16/14nm节点广泛采用,立体鳍状栅极包裹沟道,增强控制,减少漏电,提升性能。GAA(Gate-All-Around,环绕栅极): 更先进结构,如纳米片/线GAA。栅极完全包裹沟道,提供更强静电控制,望在3nm及以下节点继续提升性能和能效。

制造工艺进步是CPU性能提升基石,但难度和成本攀升,推动技术持续创新。

3.6 热设计功耗(TDP, Thermal Design Power):散热与能效

热设计功耗(TDP)是与散热和能效相关的参数,含义常被误解。

TDP的定义与实际功耗的区别: TDP官方定义通常指CPU运行典型高负载应用时,需散热系统散发掉的平均热量(瓦特W)。是给散热器和系统设计者参考的散热指标,非CPU最大功耗或实际运行功耗。CPU实际功耗随负载、频率、电压等动态变化。轻载远低于TDP;极限烤机或短时睿频(PL2/PPT)瞬时峰值功耗可能显著超TDP。

TDP对散热器选择和系统设计的影响: TDP值影响用户选散热器。TDP 65W的CPU需配至少能处理65W热量的散热器,保CPU不因过热降频。对支持更高睿频功耗或有超频需求,需选散热能力远超TDP的散热器。笔记本等散热受限设备,CPU TDP通常较低。

CPU能效比(Performance per Watt)的重要性: 随环保和移动续航要求提高,CPU能效比(单位功耗提供性能)愈发重要。优秀CPU设计应在强劲性能同时控制功耗。TDP非直接等同能效比,但可作评估功耗水平参考。

理解TDP真正含义,助正确选散热方案,合理预期CPU功耗表现。

3.7 指令集架构(ISA):软件生态的基石

指令集架构(ISA)是CPU能理解和执行的机器指令集合,是软硬件接口规范。

x86, ARM, RISC-V等主流ISA的特点与应用领域:x86 (及x86-64/AMD64): 特点:典型CISC,指令集庞大兼容性强,生态成熟。现代x86内部采类RISC微操作。应用:PC、工作站、服务器。ARM: 特点:典型RISC,低功耗高能效著称。IP授权模式,生态庞大。应用:移动设备绝对主导,嵌入式、物联网、部分服务器/笔记本扩展。RISC-V: 特点:基于RISC原则的开源ISA。开放、免费、模块化、可扩展。应用:发展初期,潜力巨大。多见于嵌入式、物联网、专用控制器,向AI加速、数据中心等探索。 其他如PowerPC, MIPS, SPARC份额相对较小。

ISA对软件兼容性与性能优化的影响: ISA决定CPU能运行的OS和应用。不同ISA通常不直接兼容(除非模拟/虚拟化,性能有损)。广泛软件生态支持的ISA竞争力更强。ISA设计也影响编译器优化和CPU执行效率。RISC规整指令和大量寄存器通常利于编译器优化。

图 9 对比x86、ARM、RISC-V

选CPU时,ISA是决定软件兼容性和生态可用性的根本因素。

3.8 思考与展望:综合评估CPU性能的挑战

评估CPU性能非易事,不能简单依赖孤立参数。

单一参数的局限性: 任何单一参数(主频、核心数、缓存大小)仅反映CPU性能某侧面。高主频不代表高性能,多核不一定适合所有应用。脱离IPC谈主频,脱离软件优化谈核心数,均片面。

面向特定应用的性能评估方法: 最科学方法是结合具体应用场景和实际基准测试(Benchmark)结果。不同应用对CPU特性需求不同:游戏玩家关注单核性能和与显卡配合;视频编辑师看重多核、大缓存、编解码指令;服务器管理员关注多核吞吐、能效、可靠性、虚拟化;嵌入式开发者可能首重功耗和成本。选择CPU时,先明确主要需求,参考专业评测和基准测试数据,结合预算综合考量。学习CPU性能参数是为了更深入理解评测结果,非简单参数堆砌。未来CPU发展将更强调针对特定负载优化和异构能力整合,使综合评估更具挑战,也更凸显基于实际应用测试的重要性。

四、CPU测试描述

本章将介绍CPU测试的目的与重要性,常用基准测试软件类型与特点,测试环境搭建注意事项,以及如何科学解读测试指标,并探讨稳定性与压力测试方法,分析CPU测试的局限性与未来发展。

4.1 CPU测试的目的与重要性

CPU测试承载多重目的,对计算机生态系统意义重大。

性能评估与横向对比: 最直接目的。通过标准化基准测试量化CPU在不同负载下性能(单核、多核、浮点、整数、内存带宽等)。数据使不同型号、品牌、架构CPU间可进行相对客观横向比较,了解性能定位和优劣。

稳定性与兼容性验证: 压力测试(Stress Test)让CPU长时间高负载运行,检验高强度工作稳定性及散热,防过热降频、死机等。兼容性测试关注CPU与主板、内存、OS、驱动、应用软件协同,确保系统稳定高效。

功耗与散热表现考察: 能效比受重视,功耗散热成测试重要环节。监测不同负载下实际功耗和核心温度,评估能效水平及对散热系统要求。对笔记本等设备尤为关键。

为软件优化和硬件设计提供反馈: 测试数据为软件开发者优化代码、硬件厂商改进设计提供反馈。开发者可据CPU特点优化算法;硬件厂商可分析瓶颈指导下代产品改进。

CPU测试是系统性工程,通过科学方法和标准流程,为理解、评估和改进CPU性能提供重要手段。

4.2 常用CPU基准测试软件介绍

众多CPU基准测试软件各有侧重,从不同维度反映CPU性能。

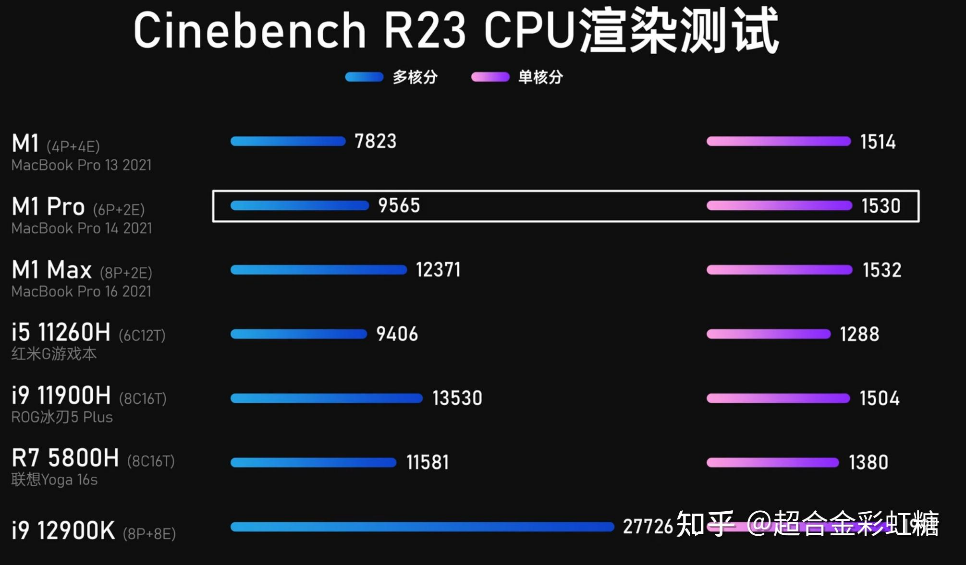

综合性能测试: 模拟多种实际应用场景负载,给出综合得分评估整体性能。Cinebench (Maxon): 基于Cinema 4D引擎,测CPU多核/单核渲染性能,反映内容创作能力。Geekbench (Primate Labs): 跨平台,含整数、浮点、加密等测试,给单核/多核分,测试时间短。PCMark (UL Solutions): 专注模拟现代办公、数字内容创作、游戏等综合场景,贴近用户实际体验。

理论运算性能测试: 测CPU纯理论计算能力(整数/浮点运算、内存带宽/延迟)。CPU-Z (CPUID): 除硬件信息外,内置Bench测CPU单/多线程能力,提供对比。AIDA64 Extreme (FinalWire): 系统信息诊断工具,“内存与缓存测试”测速与延迟;“GPGPU Benchmark”含CPU Queen(整数)、PhotoWorxx(图像处理)、ZLib(压缩)、AES(加密)、SHA3(哈希)等。

渲染与编码测试: 针对CPU在专业图形渲染和视频编码方面性能。Blender Benchmark (Blender Foundation): 基于Blender,提供官方场景测CPU/GPU渲染性能。HandBrake (Open Source): 视频转码软件,记录编码时间评估CPU视频编码效率。

游戏性能测试: CPU在游戏中负责逻辑、物理、AI等。3DMark CPU Profile (UL Solutions): 专测CPU游戏性能,评估不同线程负载下表现。游戏内置Benchmark: 许多3A游戏内置,模拟实际场景,输出帧率。测试时常配高端显卡降分辨率,减GPU瓶颈,突出CPU差异。

图 10 AIDA64界面截图

选择合适测试软件组合,理解各软件侧重,是有效CPU评测前提。专业评测常采多种软件交叉验证。

4.3 CPU测试环境搭建与注意事项

为获准确、可重复结果,搭建稳定、一致测试环境至关重要。

硬件平台的一致性: 横向对比时,除CPU(及必要主板、散热器)外其他硬件应一致。主板: 同接口CPU尽量用同型号/系列、同BIOS版本主板。内存(RAM): 同品牌、型号、容量、频率、时序,开正确XMP/EXPO。显卡(GPU): 非纯CPU测试时,用同型号高性能显卡,驱动一致,防GPU瓶颈。存储设备: 同型号高速SSD作系统盘和测试软件盘。散热器: 选能充分压制发热的散热器,防过热降频。对比测试时尽量用同款高性能散热器。电源(PSU): 功率充足、质量可靠,供稳定电力。

操作系统与驱动程序的选择与配置:操作系统(OS): 纯净安装、版本一致OS,关自动更新。驱动程序: 安装必要最新稳定版驱动,各平台一致。BIOS设置: 恢复默认优化,仅开内存XMP/EXPO。关影响性能一致性的节能或自动超频。确保功耗墙/温度墙符合规格或测试要求。

背景应用与系统服务的控制: 测试前关不必要背景应用、服务和网络连接,减CPU资源占用和干扰。系统启动后静置稳定再开始。

测试数据的记录与多次测试取平均值:数据记录: 详细记录CPU型号、主板、内存、OS、驱动、环境温度及测试结果。多次测试取平均值: 每项至少运行3-5次,去异常值后取平均。测试间给系统冷却时间。

严格控制变量,遵循规范流程,是保证CPU测试结果客观、公正、可比较的基础。

4.4 CPU测试指标解读

运行基准测试后得到数据,科学解读是关键。

单核性能分数的意义: 反映CPU单核处理单线程任务效率。对日常应用、部分游戏、系统响应速度重要。主要取决于IPC和运行频率(尤其单核睿频)。

多核性能分数的意义: 衡量CPU所有核心协同处理并行任务能力。对专业内容创作、科学计算、服务器应用、重度多任务重要。受核心数/线程数、单核性能、核间通信、缓存、内存带宽、软件优化等影响。

不同测试项目侧重点分析:整数运算密集型: CPU-Z整数测试、AIDA64 CPU Queen,反映常见计算任务性能。浮点运算密集型: AIDA64 CPU Mandel/Julia,对科学计算、工程仿真等有参考。内存带宽/延迟敏感型: AIDA64内存与缓存测试、部分压缩测试,受内存控制器、缓存、内存规格影响大。特定指令集优化型: 如用AVX优化的视频编码/科学计算,发挥支持高级指令集CPU优势。综合应用模拟型: PCMark,代表CPU日常混合应用综合表现。

图 11 消费者使用Cinebench来评估CPU

如何结合实际应用场景解读测试结果:明确需求: CPU主要用途?游戏、视频、办公?关注相关指标: 游戏关注单核和游戏场景测试;视频渲染关注多核和渲染类Benchmark。横向比较,而非绝对值: 与同价位/定位CPU或上代CPU比较更有价值。参考专业评测: 阅读可信媒体评测报告。注意“应试”现象: 有些CPU可能在特定Benchmark表现优异,但实际应用提升不明显。参考多种测试,结合实际体验。 科学解读测试指标,结合实际需求,才能发挥CPU测试指导作用。

4.5 稳定性与压力测试

除性能外,CPU长时间稳定运行也重要。

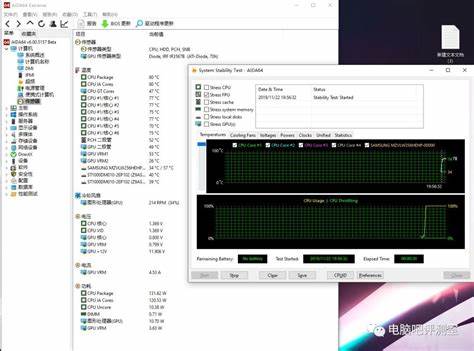

Prime95, AIDA64 System Stability Test等工具:Prime95 (GIMPS): 经典CPU压力测试,通过Mersenne素数搜索,对CPU整数/浮点单元及缓存施加极高负载。Small FFTs主考CPU核心和L1/L2,Large FFTs对内存压力大。AIDA64 System Stability Test: 内置模块,可选CPU、FPU、缓存、内存、GPU等部件压力测试。可单独或组合,实时监控参数。Stress FPU通常功耗温度很高。LinX / IntelBurnTest: 基于Linpack,对CPU浮点性能和内存系统施加巨大压力,常用於超频稳定性检验。OCCT (OverClock Checking Tool): 功能全面,提供多种CPU、GPU、内存测试模式,能检测错误。

测试时长与温度、频率监控:测试时长: 通常建议至少30分钟-1小时。追求极致稳定(如超频后)可能数小时或更长。监控: 压力测试时须用监控软件(HWiNFO, AIDA64 Sensor Panel, CPU-Z等)实时监测CPU核心温度、频率、电压、功耗、风扇转速等。

判断系统稳定性的标准:不出现错误: 测试软件报告无错误。不蓝屏、死机或自动重启。CPU温度在安全范围内: 通常远低于TJMax(95-105°C左右)。长时间高温影响寿命。CPU频率不出现大幅异常降低: 若因过热/供电不足大幅降频(Throttling),说明散热/供电有问题,即使无报错也不算完全稳定。

稳定性与压力测试是确保CPU可靠运行的必要环节,尤其在新装机、换散热、超频或系统出问题时。

4.6 学习调查研究心得:CPU测试的局限性与发展

通过学习与观察,对CPU测试的局限性及未来发展有了一些心得。

基准测试的“应试”现象: 任何标准化测试都可能面临“应试”。CPU/主板厂商可能针对特定Benchmark优化,使其获高分,但这未必完全反映广泛实际应用中的真实性能提升,导致测试结果与用户体验偏差。依赖单一或少数Benchmark评价CPU有风险,需结合多样化测试和实际体验。

AI时代对CPU测试的新需求: AI技术发展,CPU在AI推理和轻量训练中角色日重。现代CPU集成AI加速指令集(AVX-512 VNNI, AMX; ARM SVE, SME)或NPU。但主流通用CPU Benchmark对这些AI特性评估能力有限。未来需更多能有效衡量CPU在AI负载(图像识别、NLP等)下性能的标准化测试方法和工具,不仅包括峰值算力,还应考虑能效比、延迟及与软件框架协同效率。

未来CPU测试方法与工具的展望:更贴近真实应用场景: Benchmark将更注重模拟用户实际复杂交互和混合负载。异构计算能力的综合评估: 测试需全面评估整个异构系统(CPU+GPU+NPU等)协同计算能力。能效比和持续性能的权重增加: 更强调不同功耗水平性能及长时间高负载持续性能。安全特性测试的引入: 可能出现针对CPU硬件安全特性的标准化测试。AI辅助测试与智能化分析: 利用AI分析数据,识别瓶颈,预测性能,生成代表性负载。开源与社区驱动的测试标准: 可能出现更多社区驱动、标准开放的Benchmark,提高透明度和公信力。 CPU测试是不断发展完善的领域。需保持批判思维,理解现有测试优劣,关注未来趋势,才能准确把握CPU真实价值。

五、CPU知识学习心得

经过前四章系统学习,我对CPU有了更深刻全面的理解。本章分享学习心路、核心知识梳理与感悟、对CPU领域创新趋势的观察思考,展望未来图景,并为初学者提供学习建议。

5.1 我的CPU学习之旅:从迷茫到清晰

系统学习前,我对CPU认知肤浅,仅知型号主频,对其内部运作、参数关系、产业图景知之甚少,常感迷茫。

学习动机与初始认知: 动机源于对计算机底层原理的好奇及科学评价硬件性能的需求。曾简单认为“主频越高越好”、“核心数越多越强”,对IPC、缓存、指令集等概念缺乏深入理解。

学习资源与途径分享: 主要参考经典教材(《计算机组成与设计》等)、网络课程与技术文档(Coursera、Intel/AMD/ARM官网)、专业硬件评测媒体与技术论坛(AnandTech、Chiphell等)、科普视频与博客(YouTube科技UP主等)。

遇到的主要困难与克服方法:抽象概念理解: 如流水线冒险、乱序执行。通过查阅多资料、图示、脑内模拟加深理解。知识点繁杂且关联性强: 用思维导图构建知识框架,串联知识点。技术更新迭代快: 区分经典核心原理与前沿技术,掌握基础,保持好奇。理论与实践的结合: 结合实际产品参数分析,阅读评测时运用所学解读数据。 通过持续学习思考,逐渐从迷茫到清晰系统。

5.2 核心知识点梳理与个人理解深化

对CPU核心知识点有了更深层次理解。

对CPU历史演进规律的感悟: CPU发展非线性堆砌,充满选择竞争迭代。需求驱动创新(算力、低功耗、AI);生态重要性(x86/ARM成功是技术与生态胜利);“够用就好”与“追求极致”平衡(市场细分使不同设计哲学CPU共存)。

对CPU工作原理精髓的把握: CPU设计核心在于:最大化指令级并行(流水线、多发射、乱序使执行单元“忙起来”,提高IPC);最小化访存瓶颈(多级缓存、预取、缓存一致性协议弥补CPU与内存速度鸿沟);智能化预测与控制(分支预测、动态频率、智能功耗管理体现CPU“智能”适应)。

对CPU性能参数间关系的辨析: 不再孤立看待参数,理解其相互影响:主频与IPC辩证关系;核心数与单核性能权衡(大小核是体现);缓存与性能非线性关系(容量、延迟、带宽、管理策略共同决定);工艺、功耗、性能三角制约(TDP仅散热参考,实际功耗能效比结合负载架构评估)。

对CPU测试方法与数据解读能力的提升: 更理性看待Benchmark跑分:理解测试侧重点;关注测试环境一致性;警惕“应试”现象;认识测试局限性(难完全覆盖新兴场景如AI负载)。

5.3 学习调查研究心得体会:CPU领域的创新观察

关注当前CPU领域技术热点和行业趋势,形成一些思考。

对当前CPU技术热点(如Chiplet、AI加速、能效革命)的调研与思考:Chiplet(小芯片/芯粒)技术: 后摩尔时代延续性能增长和控成本有效途径。通过先进封装将不同功能小芯片互联,提高良率、降复杂度、灵活组合。AMD Ryzen/EPYC已成功应用。UCIe等开放互联标准有望构建更开放Chiplet生态。 CPU内置AI加速: 大势所趋。包括指令集扩展(Intel AVX-512 VNNI/AMX, ARM SVE2/SME矩阵乘法)和集成NPU(高通Hexagon, 苹果Neural Engine, Intel AI Boost)。专用NPU低功耗提供可观AI算力。CPU中AI加速单元如何与独立GPU/AI加速卡协同及统一编程接口是关键。能效革命: “性能不再唯一,能效才是王道”。ARM持续深耕,x86阵营拥抱大小核、精细功耗管理、新材料新晶体管(GAA)。未来CPU设计将更注重动态能效优化,可能出现更多针对特定能耗区间定制CPU。

从用户角度看CPU发展:需求与痛点分析: 用户需求多样化个性化:游戏玩家(单核、低延迟)、内容创作者(多核、大缓存、编解码加速)、办公用户(流畅性、响应、能效比)、开发者(编译、并行、指令集、虚拟化)。 用户痛点: 性能过剩与价格不匹配;信息不对称选择困难;软硬件协同不到位;升级换代成本与兼容性。

学习过程中发现的行业趋势或有趣现象: CPU厂商“垂直整合”与“开放合作”并行(苹果自研 vs RISC-V/UCIe开放);“定制化CPU”兴起(云巨头自研/定制);地缘政治影响半导体产业链;“后摩尔时代”焦虑与探索并存(架构创新、新材料、颠覆性计算范式)。

5.4 思考与展望:CPU技术的未来图景

展望CPU未来,呈现以下趋势:

摩尔定律之后,CPU将走向何方? “计算密度”和“计算效率”提升仍是主旋律。路径包括:架构创新深化;先进封装技术(2.5D/3D, Chiplet)成主流;新材料与新器件突破(碳纳米管、二维材料);超越冯·诺依曼架构探索(存内计算、神经形态计算)。

专用CPU与通用CPU的平衡与融合: 未来计算系统更依赖通用CPU核心与各种专用加速器(DSA)紧密协同。通用CPU角色演变为承担OS、调度、控制及通用计算,并注重与DSA高效交互管理。DSA针对AI、图形等特定负载更普及多样。CPU与DSA融合更紧密,或出现可编程DSA、CPU集成领域专用指令。

开源指令集(如RISC-V)的机遇与挑战: RISC-V开放、免费、模块化带来机遇:降创新门槛;促定制化差异化;推动特定领域发展(物联网、嵌入式、AI加速器)。 挑战: 生态系统成熟度(工具链、OS支持、IP核、社区)需积累;高性能高能效追赶仍需投入突破;碎片化风险需行业维护核心标准统一。

图 12 畅想CPU

我对未来理想CPU的畅想: 极致智能与自适应(动态调整架构、模式、缓存、功耗);无缝异构协同(透明高效利用异构算力);内建可信与安全(硬件级保障);高度可定制与可扩展(模块化组合);环境友好与可持续(高能效、可持续材料)。

5.5 合理化建议:面向初学者的CPU学习路径与资源推荐

为初学者提供学习路径和资源建议。

建议的学习步骤与知识模块划分:建立宏观认知: CPU作用地位、发展简史、主流品牌产品。掌握核心原理: 冯·诺依曼结构、CPU基本组成、指令周期、流水线、缓存、多核、IPC。理解性能参数与选购常识: 主频、核心数、缓存、TDP、工艺等含义影响,主流测试软件,结合需求预算解读评测选购。进阶探索: 微架构(分支预测、乱序执行)、ISA差异、新技术趋势(Chiplet, AI加速)。

推荐的优质学习资料: 入门科普: YouTube优质科技频道、图文并茂科技博客网站。系统理论: 《计算机组成原理》教材,《计算机组成与设计:硬件/软件接口》。实践与前沿: 主流CPU厂商官方文档发布会,专业硬件评测网站,技术社区论坛,RISC-V开源项目。

实践与理论结合的学习方法建议: 多看图示动画;尝试解释给别人听;关注实际产品联系理论;动手实践(虚拟机、简单超频、CPU模拟器、汇编);保持好奇与批判思维。

5.6 总结与个人展望

本次学习报告撰写是一次系统梳理、深度思考和知识升华。对CPU从诞生到精密运作,从参数到趋势,有了前所未有的敬畏和着迷。掌握了CPU核心基础,培养了多维度综合分析复杂技术问题能力,学会辨别信息、抓关键、理论联系实际。对前沿领域调研也让我对计算机体系结构未来发展有更清晰认知和浓厚兴趣。 CPU领域博大精深,本次学习仅是初步探索,在微架构细节、编译优化、OS与硬件交互、前沿计算范式等方面仍需深入。

未来计划: 深入研究特定CPU微架构;学习体系结构相关编程(汇编、底层优化);关注尝试开源硬件项目(RISC-V);持续跟踪行业动态与前沿技术(AI芯片、量子计算)。 CPU是信息技术基石,其进步改变世界。相信通过持续学习探索,能更好理解驾驭这股科技力量,为未来技术创新贡献力量。本次学习是重要里程碑,更是全新起点。